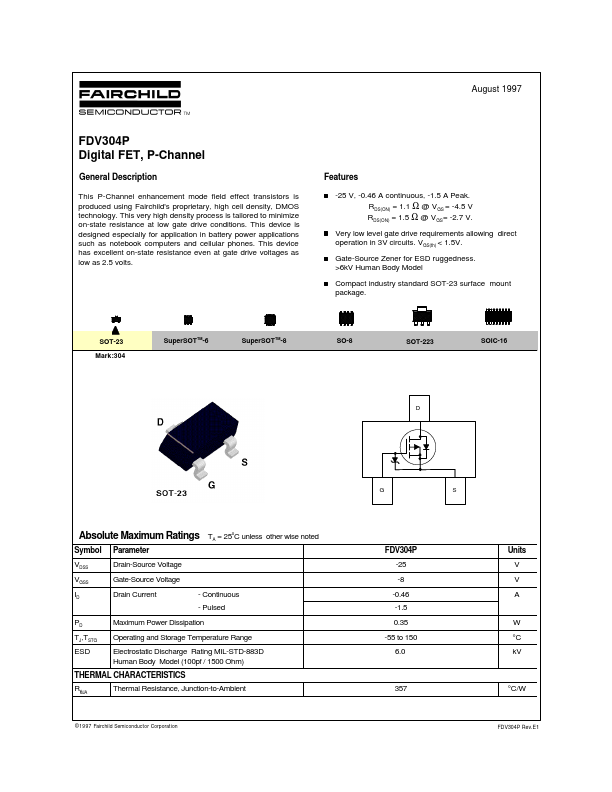

FDV304P Overview

This P-Channel enhancement mode field effect transistors is produced using Fairchild's proprietary, high cell density, DMOS technology. This very high density process is tailored to minimize on-state resistance at low gate drive conditions. This device is designed especially for application in battery power applications such as notebook puters and cellular phones.